The dual register- set makes sense as the Z8. A similar feature was present in the Datapoint 2.

0 compatible registers AF, BC, DE, HL are duplicated as two separate banks in the Z8. 0 also introduces a new signed overflow flag and complements the fairly simple 1. 6- bit IX and IY registers are primarily intended as base address- registers, where a particular instruction supplies a constant offset, but they are also usable as 1. 0 orthogonalized this a bit further by making all 1. 08.īC and DE, while HL also became usable as a 1. These early designs allowed register H and L to be paired into a 1.

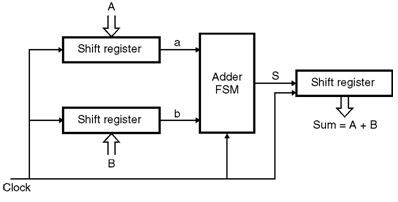

SERIAL ADDER VHDL PC

It is the PC and IR registers that are placed in a separate group, with a detachable bus segment, to allow updates of these registers in parallel with the main register bank. WZ (although the incrementer latches are also used as a 1. There is no dedicated adder for offsets or separate incrementer for R, and no need for more than a single 1. The CMOS versions also allowed low- power sleep with internal state retained, having no lower frequency limit. Although they were not intended as extra registers for general code, they were nevertheless used that way in some applications. 0 hours a week in order to meet the tight schedule given by the financial investors, according to himself. CPU, assisted by a small number of engineers and layout people. Masatoshi Shima designed most of the microarchitecture as well as the gate and transistor levels of the Z8. International Journal of Engineering Research and Applications (IJERA) is an open access online peer reviewed international journal that publishes research. Verilog Comparator example In our first verilog code, we will start with the design of a simple comparator to start understanding the Verilog language. Volt power supply.ĪSIC proven Design done FPGA proven Specification done OpenCores Certified. These companies were chosen because they could do the ion implantation needed to create the depletion- mode MOSFETs that the Z8.

6, this was formally launched onto the market. Faggin's supervision, also joined the Zilog team. Masatoshi Shima, the principal logic and transistor level- designer of the 4. He also developed the basic design methodology used for memories and microprocessors at Intel and led the work on the Intel 4. At Fairchild Semiconductor, and later at Intel, Faggin had been working on fundamental transistor and semiconductor manufacturing technology. MBaddress range, has been successfully introduced alongside the simpler Z1. 80 were designed) and the most recent Z8. In recent decades Zilog has refocused on the ever- growing market for embedded systems (for which the original Z8.

SERIAL ADDER VHDL FREE

Free research papers and research projects on FPGA recent 2014 ENGINEERING RESEARCH PAPER. The design was copied also by several Japanese, East European and Russian manufacturers.

0 was the most commonly used CPU of all time. It was also common in military applications, musical equipment, such as synthesizers, and in the computerizedcoin operatedvideo games of the late 1. CPU (and its optional support and peripheral ICs.

With the revenue from the Z8.Īccording to the designers, the primary targets for the Z8. 6, when the first fully working samples were delivered. 0 was conceived by Federico Faggin in late 1. Common manufacturer(s)Mostek, Synertek, Zilog, SGS- Thomson, NEC, Sharp, Toshiba, Rohm, Gold.

0 kommentar(er)

0 kommentar(er)